- 精準(zhǔn)測(cè)試,助力創(chuàng)新, 愛(ài)普生與南山電子攜手共

- 愛(ài)普生晶振MC-146,FC-135部分物料停產(chǎn)通知

- EPSON-NSCN晶體電路評(píng)估聯(lián)合測(cè)試中心正式運(yùn)

- 愛(ài)普生三軸加速度計(jì)傳感器HGPM01可用于無(wú)人

- 應(yīng)用于泳池機(jī)器人的慣性導(dǎo)航高性能陀螺儀傳

- 愛(ài)普生三軸加速度傳感器M-A352AD10可用于橋

- 愛(ài)普生發(fā)布全新TCXO溫補(bǔ)晶振TG5032系列和TG

- 愛(ài)普生陀螺儀傳感器XV7021BB完整數(shù)據(jù)表可用

- WürthElektronik伍爾特推出溫度穩(wěn)健的精密

低噪音晶振電路設(shè)計(jì)指南

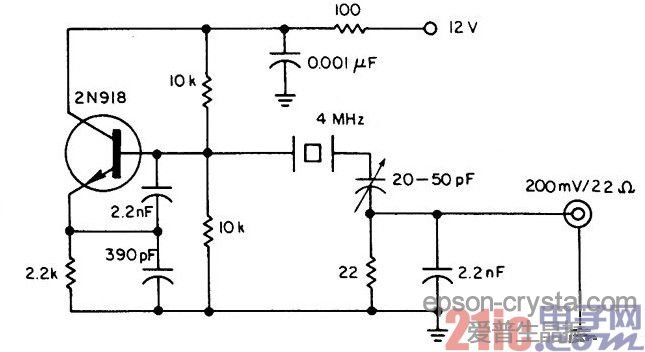

下面是一個(gè)愛(ài)普生晶體振蕩器電路圖,該振蕩器的輸出具有高光譜純度,并且很穩(wěn)定。晶體管除了決定振蕩器的頻率,還可用作一個(gè)不期望諧波的低通濾波器,和邊帶噪音的帶通濾波器。噪音帶寬限制在低于100Hz。所有更高的諧波實(shí)際上為4MHz的基本振蕩頻率的第三諧波抑制60dB。石英晶體振蕩器是信號(hào)源的核心所在。在構(gòu)建各種電子設(shè)備及通信系統(tǒng)設(shè)備等過(guò)程中,石英晶體振蕩器周圍的電路結(jié)構(gòu)及設(shè)計(jì)對(duì)系統(tǒng)能否較大程度發(fā)揮功能起著重要的作用。特別是石英晶體振蕩器周圍電路,由于將在搭載數(shù)字電路的基板上以較高速度開(kāi)關(guān)工作,較易產(chǎn)生噪音,所以設(shè)計(jì)電路之際必須對(duì)此十分注意。作為降低噪音電路設(shè)計(jì)的指南,本文將就使使用石英晶體振蕩器的周圍電路設(shè)計(jì)中的噪音對(duì)策進(jìn)行解說(shuō)。

-

2025-10-14愛(ài)普生SG2520EHN差分晶振:為5G與400G通信量身打造的高

-

2025-09-22愛(ài)普生數(shù)字輸出型陀螺儀XV7081BB,±400°/s量程,用于自

-

2025-09-17愛(ài)普生HCSL輸出晶體振蕩器SG3225HBN,頻率范圍100MHz~32

466009906

466009906